# 1.0 – 6 GHz Ultra Low Noise Amplifier

#### **Features**

Frequency Range: 1.0- 6 GHz0.7 dB mid-band Noise Figure

18 dB mid band Gain

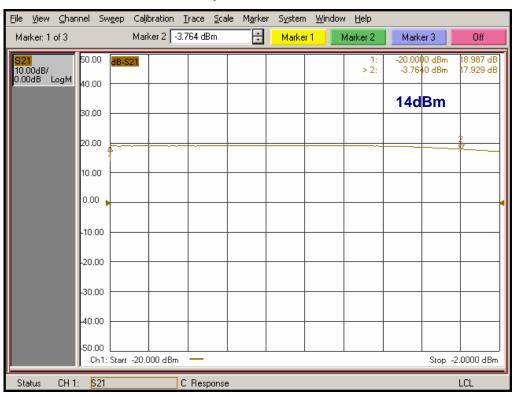

14dBm Nominal P1dB

Bias current : 50mA

0.15-um InGaAs pHEMT Technology

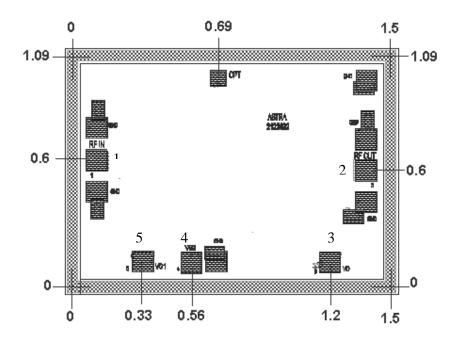

Chip Size: 1.5 mm x 1.1 mm x 0.1 mm

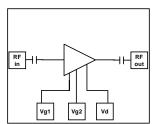

#### **Functional Diagram**

#### **Typical Applications**

- Cellular system

- Base stations

- Applications from 1 to 6GHz in Balanced configuration

- Communication receivers and transmitters.

### **Description**

AMT 2122092 is an Ultra Low Noise single stage Amplifier MMIC combining high gain and state of the art noise figure. No-off-chip components are needed, except for additional bypass capacitors in DC bias path for reliable operation. Matching network, DC Blocks and bypass capacitors are provided on-chip for simplification of assembly operation. The amplifier operates on Drain Bias of +5V and Gate biases of +2V & -0.4 V supply. The bias current can be tuned from 30 to 70 mA as per requirement with minor variation in performance. The LNA features 18dB mid-band gain and 0.7 dB mid-band noise figure (typical). The die is fabricated using reliable Low noise 0.15um InGaAs pHEMT process.

## **Absolute Maximum Ratings** (1)

| Parameter             | Absolute Maximum | Units |

|-----------------------|------------------|-------|

| Positive DC Supply    | 12               | V     |

| RF Input Power        | 23               | dBm   |

| Supply current        | 100              | mA    |

| Operating Temperature | -55 to +85       | °C    |

| Storage Temperature   | -65 to +150      | °C    |

1. Operation beyond these limits may cause permanent damage to the component

## Electrical Specifications <sup>(1)</sup> @ $T_A$ = 25 °C, $Z_o$ =50 $\Omega$ Vdd = +5V, Vg1= -0.4V, Vg2= +2V

| Parameter                                                 | Min. | Тур.  | Max.  | Units |  |

|-----------------------------------------------------------|------|-------|-------|-------|--|

| Frequency                                                 | 1.0  | -     | 6     | GHz   |  |

| RF Performance between 2.5-4 GHz unless otherwise stated: |      |       |       |       |  |

| Gain                                                      | 17   | 18    | 20    | dB    |  |

| Gain Flatness                                             | -    | ± 0.5 | ± 0.7 | dB    |  |

| Noise Figure                                              | 0.6  | 0.7   | .8    | dB    |  |

| Input Return Loss                                         | -6   | -8    | -     | dB    |  |

| Output Return Loss                                        | -10  | -15   | -     | dB    |  |

| Reverse Isolation                                         | -    | -31   | -     | dB    |  |

| Output Power (P1dB) @ 3.3 GHz                             | -    | +14   | -     | dBm   |  |

| Output Third Order Intercept(IP3) (2)                     | -    | 30    | -     | dBm   |  |

| Supply Current <sup>(3)</sup>                             | 30   | 50    | 70    | mA    |  |

#### Note:

- 1. Electrical specifications as measured in test fixture.

- 2. Estimated value

- 3. Supply current tunable with gate bias (Vg1) with minor variation in performance.

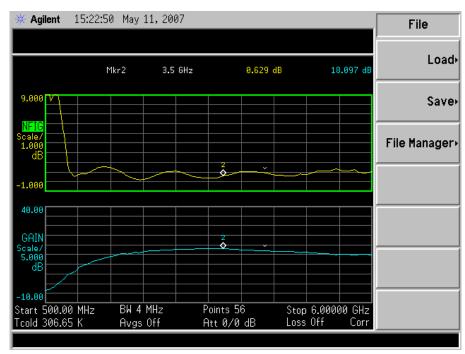

#### **Test fixture data**

Vdd = +5V, Vg1 = -0.4V, Vg2 = +2V, Total Current = 50mA,  $T_A = 25$   $^{\circ}C$

#### Noise Figure & Gain performance in 0.5-6GHz

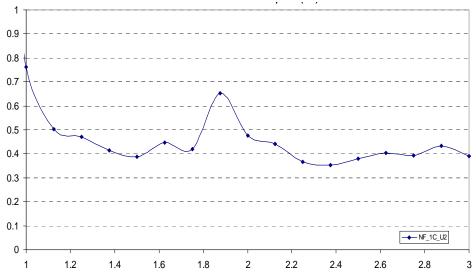

#### Noise Figure performance in 1 - 3 GHz

Astra Microwave Products Limited, Hyderabad, INDIA

Test fixture data

Vdd = +5V, Vg1 = -0.4V, Vg2 = +2V, Total Current = 50mA,  $T_A = 25$  °C

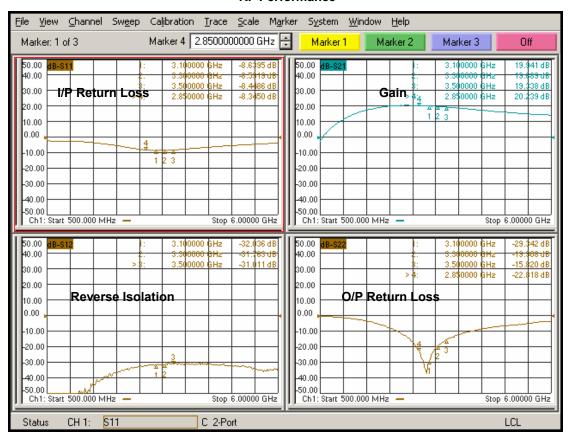

#### **RF Performance**

#### **Test fixture data**

Vdd = +5V, Vg1 = -0.4V, Vg2 = +2V, Total Current = 50mA,  $T_A = 25$  °C

#### Gain compression at 3.3 GHz

## **Mechanical Characteristics**

**Units:** millimeters

#### Note:

1. All RF and DC bond pads are 100μm x 100μm

2. Pad no. 1: RF In

3. Pad no. 2 : RF Out

4. Pad no. 3: Vdd (470 pF)

5. Pad no. 4: Vg2 (470pF)

6. Pad no. 5: Vg1 (470pF)

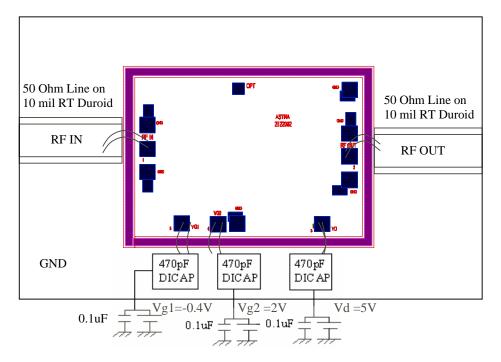

## **Recommended Assembly Diagram**

#### Note:

- 1. Two one mil (0.0254mm) bond wires of minimum length should be used for RF input and Output.

- Two one mil (0.0254mm) bond wires of minimum length should be used from chip bond pad to 470pF bypass capacitors.

- 0.1uF capacitor should be additionally used as second level of bypass for reliable operation.

- 4. All capacitors shown in the assembly diagram (except  $0.1\mu F$ ) are single layer capacitors.

**Die attach:** For Epoxy attachment, use of a two-component conductive epoxy is recommended. An epoxy fillet should be visible around the total die periphery. If Eutectic attachment is preferred, use of fluxless AuSn (80/20) 1-2 mil thick preform solder is recommended. Use of AuGe preform should be strictly avoided.

Wire bonding: For DC pad connections use either ball or wedge bonds. For best RF performance, use of  $250\mu$ m length of wedge bonds is advised. Single Ball bonds of  $250-300\mu$ m though acceptable, may cause a deviation in RF performance.

GaAs MMIC devices are susceptible to Electrostatic discharge. Proper precautions should be observed during handling, assembly & testing

All information and Specifications are subject to change without prior notice